–°—А–Њ—З–љ–∞—П –њ—Г–±–ї–Є–Ї–∞—Ж–Є—П –љ–∞—Г—З–љ–Њ–є —Б—В–∞—В—М–Є

+7 995 770 98 40

+7 995 202 54 42

info@journalpro.ru

–Я–Њ—Б—В—А–Њ–µ–љ–Є–µ —Г–њ—А–∞–≤–ї—П—О—Й–Є—Е –∞–≤—В–Њ–Љ–∞—В–Њ–≤ –і–ї—П —Б—Е–µ–Љ —Б–Є–љ—Е—А–Њ–љ–љ—Л—Е —Ж–Є—Д—А–Њ–≤—Л—Е –∞–≤—В–Њ–Љ–∞—В–Њ–≤

–†—Г–±—А–Є–Ї–∞: –Ґ–µ—Е–љ–Є—З–µ—Б–Ї–Є–µ –љ–∞—Г–Ї–Є

–Ц—Г—А–љ–∞–ї: «–Х–≤—А–∞–Ј–Є–є—Б–Ї–Є–є –Э–∞—Г—З–љ—Л–є –Ц—Г—А–љ–∞–ї вДЦ5 2017» (–Љ–∞–є, 2017)

–Ъ–Њ–ї–Є—З–µ—Б—В–≤–Њ –њ—А–Њ—Б–Љ–Њ—В—А–Њ–≤ —Б—В–∞—В—М–Є: 3626

–Я–Њ–Ї–∞–Ј–∞—В—М PDF –≤–µ—А—Б–Є—О –Я–Њ—Б—В—А–Њ–µ–љ–Є–µ —Г–њ—А–∞–≤–ї—П—О—Й–Є—Е –∞–≤—В–Њ–Љ–∞—В–Њ–≤ –і–ї—П —Б—Е–µ–Љ —Б–Є–љ—Е—А–Њ–љ–љ—Л—Е —Ж–Є—Д—А–Њ–≤—Л—Е –∞–≤—В–Њ–Љ–∞—В–Њ–≤

–Р–љ—В–Є–Ї –Ь–Є—Е–∞–Є–ї –Ш–ї—М–Є—З,

–і–Њ—Ж–µ–љ—В –Ї–∞—Д–µ–і—А—Л –Т—Л—З–Є—Б–ї–Є—В–µ–ї—М–љ–Њ–є —В–µ—Е–љ–Є–Ї–Є

–Ь–Њ—Б–Ї–Њ–≤—Б–Ї–Њ–≥–Њ —В–µ—Е–љ–Њ–ї–Њ–≥–Є—З–µ—Б–Ї–Њ–≥–Њ —Г–љ–Є–≤–µ—А—Б–Є—В–µ—В–∞

–†–Њ–Љ–∞–љ–Њ–≤ –Р–ї–µ–Ї—Б–∞–љ–і—А –Ь–Є—Е–∞–є–ї–Њ–≤–Є—З,

–і–Њ—Ж–µ–љ—В –Ї–∞—Д–µ–і—А—Л –Т—Л—З–Є—Б–ї–Є—В–µ–ї—М–љ–Њ–є —В–µ—Е–љ–Є–Ї–Є

–Ь–Њ—Б–Ї–Њ–≤—Б–Ї–Њ–≥–Њ —В–µ—Е–љ–Њ–ї–Њ–≥–Є—З–µ—Б–Ї–Њ–≥–Њ —Г–љ–Є–≤–µ—А—Б–Є—В–µ—В–∞

–Р–Э–Э–Ю–Ґ–Р–¶–Ш–ѓ

–†–∞—Б—Б–Љ–∞—В—А–Є–≤–∞—О—В—Б—П –≤–Њ–њ—А–Њ—Б—Л –њ–Њ—Б—В—А–Њ–µ–љ–Є—П —Г–њ—А–∞–≤–ї—П—О—Й–Є—Е –∞–≤—В–Њ–Љ–∞—В–Њ–≤ —Б—Е–µ–Љ —Б–Є–љ—Е—А–Њ–љ–љ—Л—Е —Ж–Є—Д—А–Њ–≤—Л—Е –∞–≤—В–Њ–Љ–∞—В–Њ–≤. –Я—А–µ–і–ї–∞–≥–∞–µ—В—Б—П –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ —Б—Е–µ–Љ —Б —П–≤–љ—Л–Љ —Г–Ї–∞–Ј–∞–љ–Є–µ–Љ –∞–ї—М—В–µ—А–љ–∞—В–Є–≤–љ—Л—Е –∞–і—А–µ—Б–Њ–≤ –Њ–њ–µ—А–∞–љ–і–Њ–≤ —Б —Ж–µ–ї—М—О —Б–Њ–Ї—А–∞—Й–µ–љ–Є—П –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Л—Е –∞–њ–њ–∞—А–∞—В–љ—Л—Е —Б—А–µ–і—Б—В–≤.

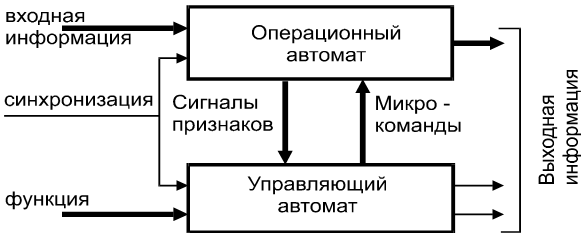

–Я—А–Є –њ—А–Њ–µ–Ї—В–Є—А–Њ–≤–∞–љ–Є–Є –≤—Л—З–Є—Б–ї–Є—В–µ–ї—М–љ–Њ–≥–Њ —Г—Б—В—А–Њ–є—Б—В–≤–∞, –≤—Л–њ–Њ–ї–љ—П—О—Й–µ–≥–Њ —Б–ї–Њ–ґ–љ—Г—О –Њ–±—А–∞–±–Њ—В–Ї—Г —Ж–Є—Д—А–Њ–≤–Њ–є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –њ–Њ –Ј–∞–і–∞–љ–љ–Њ–Љ—Г –∞–ї–≥–Њ—А–Є—В–Љ—Г, –Њ–і–љ–Є–Љ –Є–Ј –≤–∞—А–Є–∞–љ—В–Њ–≤ –і–µ–Ї–Њ–Љ–њ–Њ–Ј–Є—Ж–Є–Є —П–≤–ї—П–µ—В—Б—П –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ–Є–µ —Б–Є–љ—Е—А–Њ–љ–љ–Њ–≥–Њ –≤—Л—З–Є—Б–ї–Є—В–µ–ї—П –≤ –≤–Є–і–µ –Ї–Њ–Љ–њ–Њ–Ј–Є—Ж–Є–Є –і–≤—Г—Е

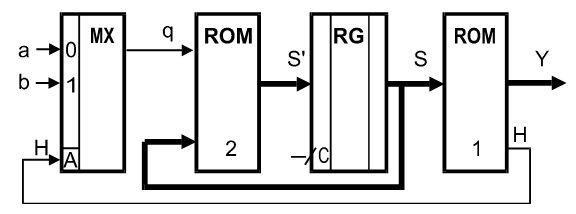

–†–Є—Б.1. –°—В—А—Г–Ї—В—Г—А–∞ –≤—Л—З–Є—Б–ї–Є—В–µ–ї—П

–∞–≤—В–Њ–Љ–∞—В–Њ–≤ –Њ–њ–µ—А–∞—Ж–Є–Њ–љ–љ–Њ–≥–Њ –Є —Г–њ—А–∞–≤–ї—П—О—Й–µ–≥–Њ вАФ —А–Є—Б.1. –Я—А–Є —Н—В–Њ–Љ –Њ–њ–µ—А–∞—Ж–Є–Њ–љ–љ—Л–є –∞–≤—В–Њ–Љ–∞—В —А–µ–∞–ї–Є–Ј—Г–µ—В –Њ—В–і–µ–ї—М–љ—Л–µ —И–∞–≥–Є –∞–ї–≥–Њ—А–Є—В–Љ–∞, –∞ —Г–њ—А–∞–≤–ї—П—О—Й–Є–є –∞–≤—В–Њ–Љ–∞—В —А–µ–∞–ї–Є–Ј—Г–µ—В –њ–Њ—А—П–і–Њ–Ї –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П —И–∞–≥–Њ–≤ –∞–ї–≥–Њ—А–Є—В–Љ–∞ /1/.

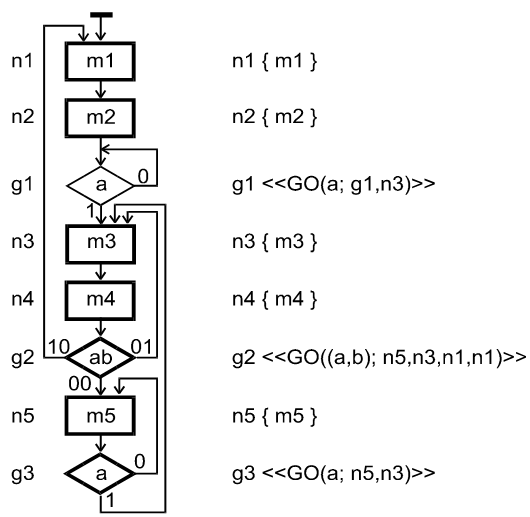

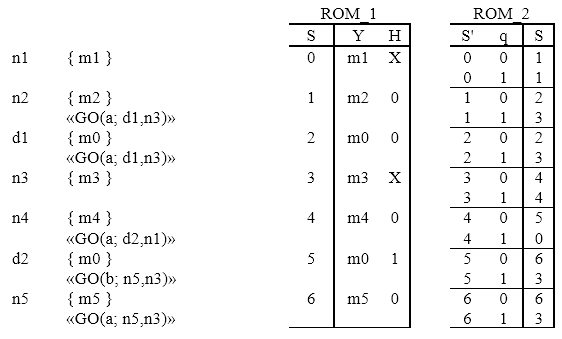

–С—Г–і–µ–Љ —А–∞—Б—Б–Љ–∞—В—А–Є–≤–∞—В—М —А–∞–±–Њ—В—Г —Г–њ—А–∞–≤–ї—П—О—Й–Є—Е –∞–≤—В–Њ–Љ–∞—В–Њ–≤, –і–µ–Љ–Њ–љ—Б—В—А–Є—А—Г—О—Й–Є–µ –Њ—Б–љ–Њ–≤–љ—Л–µ –њ—А–Є–Љ–µ–љ—П–µ–Љ—Л–µ –≤–∞—А–Є–∞–љ—В—Л –∞–і—А–µ—Б–∞—Ж–Є–Є –Љ–Є–Ї—А–Њ–Є–љ—Б—В—А—Г–Ї—Ж–Є–є, –љ–∞ –∞–ї–≥–Њ—А–Є—В–Љ–µ, –њ–Њ–Ї–∞–Ј–∞–љ–љ–Њ–Љ –љ–∞ —А–Є—Б. 2

–†–Є—Б2. –С–ї–Њ–Ї-—Б—Е–µ–Љ–∞ –Є –±–ї–Њ–Ї-—В–µ–Ї—Б—В –Љ–Є–Ї—А–Њ–њ—А–Њ–≥—А–∞–Љ–Љ—Л

–†–∞—Б—Б–Љ–Њ—В—А–Є–Љ —А–∞–±–Њ—В—Г —Г–њ—А–∞–≤–ї—П—О—Й–µ–≥–Њ –∞–≤—В–Њ–Љ–∞—В–∞ —Б –∞–і—А–µ—Б–љ—Л–Љ –Я–Ч–£. –Т —Г–њ—А–∞–≤–ї—П—О—Й–µ–Љ –∞–≤—В–Њ–Љ–∞—В–µ —Б –∞–і—А–µ—Б–љ—Л–Љ –Я–Ч–£ (ROM_1), —А–µ–∞–ї–Є–Ј—Г—О—Й–µ–Љ —Д—Г–љ–Ї—Ж–Є—О –≤—Л—Е–Њ–і–∞, —Б–ї–µ–і—Г–µ—В —А–∞–Ј–Љ–µ—Б—В–Є—В—М –Љ–Є–Ї—А–Њ–Ї–Њ–Љ–∞–љ–і—Л; –њ—А–Є —Н—В–Њ–Љ –Є—Е —А–∞—Б–њ—А–µ–і–µ–ї–µ–љ–Є–µ –њ–Њ –Њ–њ—А–µ–і–µ–ї–µ–љ–љ—Л–Љ –∞–і—А–µ—Б–∞–Љ —Б–Њ–≤–µ—А—И–µ–љ–љ–Њ –њ—А–Њ–Є–Ј–≤–Њ–ї—М–љ–Њ, –Ј–∞ –Є—Б–Ї–ї—О—З–µ–љ–Є–µ–Љ –љ–∞—З–∞–ї—М–љ–Њ–є –Љ–Є–Ї—А–Њ–Ї–Њ–Љ–∞–љ–і—Л, –Ї–Њ—В–Њ—А–∞—П –і–Њ–ї–ґ–љ–∞ —А–∞—Б–њ–Њ–ї–∞–≥–∞—В—М—Б—П –њ–Њ –љ—Г–ї–µ–≤–Њ–Љ—Г –∞–і—А–µ—Б—Г –≤ —Б–Є–ї—Г –≤—Л—И–µ—Г–Ї–∞–Ј–∞–љ–љ–Њ–≥–Њ –Њ–≥—А–∞–љ–Є—З–µ–љ–Є—П (—Б–±—А–Њ—Б –≤ –љ–Њ–ї—М RG –£–Р –≤ –љ–∞—З–∞–ї—М–љ—Л–є –Љ–Њ–Љ–µ–љ—В –≤—А–µ–Љ–µ–љ–Є). –Я–Ч–£ (ROM_2), —А–µ–∞–ї–Є–Ј—Г—О—Й–µ–µ —Д—Г–љ–Ї—Ж–Є—О –њ–µ—А–µ—Е–Њ–і–Њ–≤ –∞–≤—В–Њ–Љ–∞—В–∞, –Љ–Њ–ґ–љ–Њ —В—А–∞–Ї—В–Њ–≤–∞—В—М –Ї–∞–Ї –∞–і—А–µ—Б–љ–Њ–µ –Я–Ч–£. –ѓ—З–µ–µ–Ї –≤ –∞–і—А–µ—Б–љ–Њ–Љ –Я–Ч–£ –≤ –і–≤–∞ —А–∞–Ј–∞ –±–Њ–ї—М—И–µ, —З–µ–Љ –≤ –Я–Ч–£ –Љ–Є–Ї—А–Њ–Ї–Њ–Љ–∞–љ–і. –Ъ–∞–ґ–і–Њ–є —П—З–µ–є–Ї–µ –Я–Ч–£ –Љ–Є–Ї—А–Њ–Ї–Њ–Љ–∞–љ–і —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—В –і–≤–µ —П—З–µ–є–Ї–Є –≤ –∞–і—А–µ—Б–љ–Њ–Љ –Я–Ч–£, –≤ –Ї–Њ—В–Њ—А—Л—Е –Ј–∞–њ–Є—Б—Л–≤–∞—О—В—Б—П –і–≤–∞ –∞–ї—М—В–µ—А–љ–∞—В–Є–≤–љ—Л—Е –∞–і—А–µ—Б–∞.

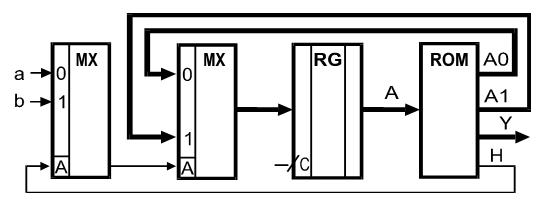

–†–Є—Б.3. –£–Р —Б –∞–і—А–µ—Б–љ—Л–Љ –Я–Ч–£; –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ—Л–є –≤–∞—А–Є–∞–љ—В

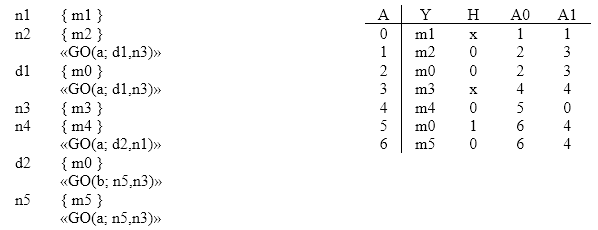

–С–Њ–ї–µ–µ —Н–Ї–Њ–љ–Њ–Љ–Є—З–љ–Њ–є —П–≤–ї—П–µ—В—Б—П —Б—Е–µ–Љ–∞ —Б —П–≤–љ—Л–Љ —Г–Ї–∞–Ј–∞–љ–Є–µ–Љ –∞–ї—М—В–µ—А–љ–∞—В–Є–≤–љ—Л—Е –∞–і—А–µ—Б–Њ–≤. –≠—В–∞ —Б—Е–µ–Љ–∞ –Њ—В–ї–Є—З–∞–µ—В—Б—П –Њ—В –њ—А–µ–і—Л–і—Г—Й–µ–є —В–µ–Љ, —З—В–Њ, –њ–Њ —Б—Г—Й–µ—Б—В–≤—Г, —В–Њ—В –ґ–µ —Б–њ–Њ—Б–Њ–± –∞–і—А–µ—Б–∞—Ж–Є–Є –≤—Л–њ–Њ–ї–љ–µ–љ —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ —В–Њ–ї—М–Ї–Њ –Њ–і–љ–Њ–≥–Њ –Я–Ч–£. –Т —Н—В–Њ–Љ –≤–∞—А–Є–∞–љ—В–µ –∞–ї—М—В–µ—А–љ–∞—В–Є–≤–љ—Л–µ –∞–і—А–µ—Б–∞ –Ј–∞–њ–Є—Б—Л–≤–∞—О—В—Б—П –≤ —В–Њ–є –ґ–µ –Љ–Є–Ї—А–Њ–Є–љ—Б—В—А—Г–Ї—Ж–Є–Є, —З—В–Њ –Є –Љ–Є–Ї—А–Њ–Ї–Њ–Љ–∞–љ–і–∞

–†–Є—Б.4. –£–Р —Б —П–≤–љ—Л–Љ —Г–Ї–∞–Ј–∞–љ–Є–µ–Љ –∞–ї—М—В–µ—А–љ–∞—В–Є–≤–љ—Л—Е –∞–і—А–µ—Б–Њ–≤

–Ґ–∞–±–ї–Є—Ж–∞ –њ–µ—А–µ—Е–Њ–і–Њ–≤ –і–ї—П —Н—В–Њ–є —Б—Е–µ–Љ—Л –њ—А–Є–≤–µ–і–µ–љ–∞ –і–∞–ї–µ–µ.

–Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, –њ—А–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–Є –∞–ї—М—В–µ—А–љ–∞—В–Є–≤–љ–Њ–є –∞–і—А–µ—Б–∞—Ж–Є–Є –Љ–Њ–ґ–љ–Њ –Ј–љ–∞—З–Є—В–µ–ї—М–љ–Њ —Б–Њ–Ї—А–∞—В–Є—В—М –Њ–±—К–µ–Љ –∞–њ–њ–∞—А–∞—В–љ—Л—Е —Б—А–µ–і—Б—В–≤, –љ–µ–Њ–±—Е–Њ–і–Є–Љ—Л—Е –і–ї—П –њ–Њ—Б—В—А–Њ–µ–љ–Є—П —Г–њ—А–∞–≤–ї—П—О—Й–Є—Е –∞–≤—В–Њ–Љ–∞—В–Њ–≤ —Б–Є–љ—Е—А–Њ–љ–љ—Л—Е —Ж–Є—Д—А–Њ–≤—Л—Е –∞–≤—В–Њ–Љ–∞—В–Њ–≤..

–Ы–Є—В–µ—А–∞—В—Г—А–∞

- –Ъ–∞—А–њ–Њ–≤ –Ѓ.–У. –Ґ–µ–Њ—А–Є—П –∞–≤—В–Њ–Љ–∞—В–Њ–≤. –£—З–µ–±–љ–Є–Ї –і–ї—П –≤—Г–Ј–Њ–≤ вАФ –Я–Ш–Ґ–Х–†, 2002, 206—Б.